设计一个4选1多路选择器。

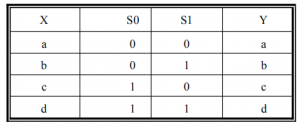

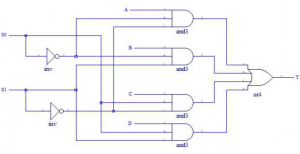

4选1多路选择器,即从输入的四个数据中选择其中一个。通过定义两个变量,产生四种状态,分别对应四个数据的输出。由此可得到如下真值表。将输入的a,b,c,d,s0,s1和输出Y的关系写成逻辑表达式则打得到:

Y=a(s0’s1’)+b(s0’s1)+c(s0s1’)+d(s0s1)

4选1多路选择器程序清单mult4.v

module mult4 ( input wire a, //定义四位输入 input wire b, input wire c, input wire d, input wire [1:0] sel, //定义输出的选择变量 output reg led //定义选择器输出结果对应的led ); always@(sel) //根据sel结果选择输出,当sel变化时执行 begin case(sel) 2'b00: led = a; 2'b01: led = b; 2'b10: led = c; 2'b11: led = d; endcase end endmodule

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。